L'HyperTransport è stato creato per ridurre considerevolmente i colli di bottiglia dovuti a Bus antiquati, incapaci ormai di stare dietro alle CPU più recenti. Quando il progetto relativo all'HT fu deciso (seconda metà degli anni '90), vi erano già in commercio processori con una frequenza superiore ai 700 MHz, i quali però dovevano limitarsi ad un FSB di 133 MHz, a causa dei Bus PCI (66MHz) e AGP (100 MHz). Un FSB più elevato avrebbe portato pochi vantaggi se rapportati al costo di implementazione.

HyperTransport, grazie alla propria scalabilità, all'essere una connessione seriale (point-to-point) e non parallela, avrebbe provveduto a superare queste limitazioni, soprattutto nei settori embedded ed enterprise. L'idea era semplice.

Prima di tutto lo si sarebbe reso compatibile con tutti i Bus di I/O fino ad allora esistenti, così da garantirne la massima espansione commerciale. Per questo motivo l'HT sarebbe stato modulare. Il canale di comunicazione avrebbe potuto operare (inizialmente) in un range di frequenza tra i 200 e gli 800 MHz, mentre l'ampiezza di canale sarebbe stata a scelta tra i 2 e i 32 Bit (meno Bit erano necessari, meno sarebbe costato il disegno di quel canale sulla scheda madre). In questo modo sarebbe stato possibile utilizzare l'HT con tutti i Bus esistenti. Ad esempio, un Bus HT a 16 Bit operante a 800 MHz avrebbe potuto garantire una banda bidirezionale di 25.6 Gb/s, in grado di reggere il traffico dati di due controller Ethernet di classe Gigabit (10 Gb/s ognuno). Questo avrebbe eliminato completamente il collo di bottiglia dei Bus PCI (133 MB/s) e PCI-X (1064 MB/s), non solo più lenti, ma anche molto più costosi da implementare sul PCB delle schede madri.

"HyperTransport System Architecture", di Don Anderson e Jay Trodden

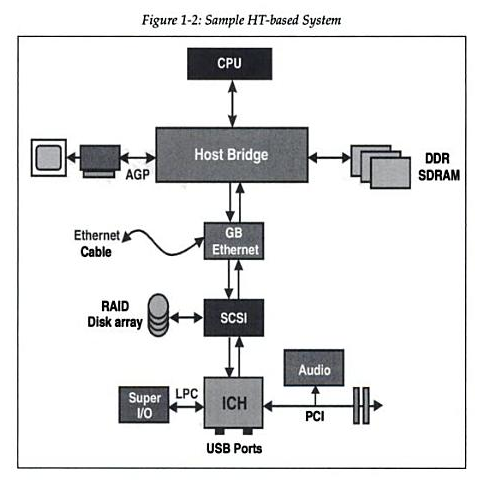

Non solo poteva garantire una minore latenza, ed una maggiore banda dati, ma l'HT poteva gestire un maggior numero di periferiche contemporaneamente. Il Bus PCI-X poteva gestire una periferica, il Bus PCI quattro contemporaneamente. L'HT, grazie al tunneling1, ne poteva gestire fino a 31, senza la necessità di un NorthBridge! Le uniche periferiche che sarebbero dovute passare attraverso il SouthBridge sarebbero state quelle di massa (EIDE e SATA), Audio e USB. CPU, memoria Ram, Scheda Video, CTRL SCSI e schede di rete avrebbero potuto comunicare tra loro attraverso un canale velocissimo e a bassissima latenza.

Network World, Luglio 2001

Grazie all'HyperTransport AMD non solo avrebbe avuto un Bus capace di far comunicare in maniera diretta e veloce le CPU in un sistema Multi Socket, ma avrebbe permesso un traffico dati diretto e veloce anche tra le CPU e le periferiche di quel sistema, senza che fosse necessario riscrivere il software. HyperTransport era infatti perfettamente retrocompatibile.

Il tutto a costi ridicolosamente bassi: essendo un sistema point-to-point, il disegno delle schede madri poté essere semplificato, diminuendone i costi di produzione. Una caratteristica che in ambito embedded e server è molto ricercata, a causa delle economie di scala.

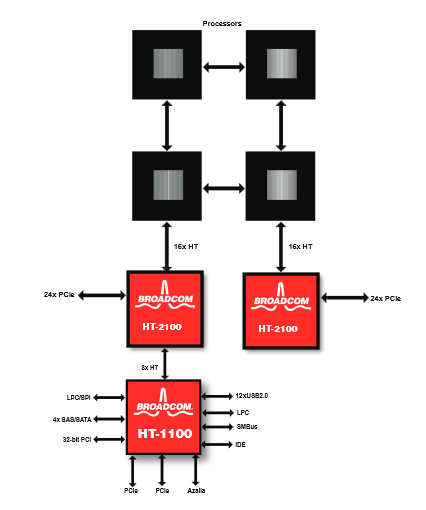

1- Con "Tunneling" ci si riferisce alla possibilità di utilizzare il Bus HT per collegare tra loro due o più CTRL, a cascata. Un esempio è riportato nello schema qui sotto, relativo al chipset HT-2100 di Broadcom, in comunicazione con il CTRL HT-1100 (SouthBridge).