Vishera come e meglio di Bulldozer

Piledriver parte dagli stessi concetti di Bulldozer, anzi ne rappresenta "solo" un'evoluzione. AMD ha ripreso esattamente i concetti introdotti con la sua precedente architettura per le CPU desktop x86 top di gamma apportando ottimizzazioni in ogni dove. Con Piledriver, dunque, viene indicata l'architettura dei core delle CPU FX-series 2012 note con il nome in codice di Vishera e disponibili con architettura a 4, 6 e 8 core o, per meglio dire, a 2, 3 e 4 moduli (come per Bulldozer, un modulo è l'unità minima delle CPU FX).

Pur senza entrare nuovamente nel dettaglio e nelle definizioni di "core" e "module", cose delle quali abbiamo più volte parlato, vi ricordiamo che un modulo Bulldozer include due core x86 che condividono parte delle risorse quali la cache L2, l'unità FPU capace di gestire anche istruzioni FMAC a 256-bit e le unità di Fetch e Decode.

Nel dettaglio, queste sono le caratteristiche dell'architettura Vishera:

| Caratteristiche di base delle CPU in esame | |||||

| AMD Vishera (8-core) |

AMD Zambezi (8-core) |

Intel SB (4-core) |

Intel SB-E (6-core) |

Intel IB (4-core) |

|

| Architettura | Piledriver | Bulldozer | Sandy Bridge | Sandy Bridge | Ivy Bridge |

| Socket | AM3+ | AM3+ | LGA 1155 | LGA 2011 | LGA 1155 |

| Numero di transistor | 1,2 miliardi | 1,2 miliardi | 1,16 miliardi | 2,27 miliardi | 1,4 miliardi |

| Processo produttivo | 32nm SOI | 32nm SOI | 32nm | 32nm | 22nm |

| Dimensioni die | ~315mm2 | ~315mm2 | 216mm2 | 435mm2 | 160mm2 |

| Cache L1 | 16KB D per core 64KB I per modulo |

16KB D per core 64KB I per modulo |

32KB D per core 32KB I per core |

32KB D per core 32KB I per core |

32KB D per core 32KB I per core |

| Cache L2 | 2MB per modulo | 2MB per modulo | 256KB per core | 256KB per core | 256KB per core |

| Cache L3 | 8MB | 8MB | 8MB | Fino a 15MB | 8MB |

| Thread per core | 1 | 1 | 2 | 2 | 2 |

| Turbo | Si | Si | Si | Si | Si |

| FPU | 256-bit | 256-bit | 128-bit | 128-bit | 128-bit |

| Controller delle memorie | DDR3-1866 Dual-channel |

DDR3-1866 Dual-channel |

DDR3-1333 Dual-channel |

DDR3-1600 Quad-channel |

DDR3-1600 Dual-channel |

| Controller grafico | N/A | N/A | DirectX 10.1 | N/A | DirectX 11 |

| PCI Express | N/A | N/A | 16 lane (2.0) | 40 lane (3.0) | 16 lane (3.0) |

| TDP | 95W, 125W | 95W, 125W | 65W, 95W | 130W | 77W |

Vishera è prodotto esattamente con lo stesso nodo di Bulldozer, quello a 32nm con tecnologia SOI (Silicon on Insulator) di GlobalFoundries. Il numero di transistor resta esattamente identico a quello del suo antenato così come l'occupazione di spazio sul die: questa effettivamente poteva essere una delle possibili ottimizzazioni sulle quali evidentemente AMD non è risucita a fare molto.

Come dicevamo anche in passato, AMD deve migliorare nettamente il suo design per poter raggiungere il livello della rivale Intel che riesce a mettere quasi lo stesso numero di transistor in un'area nettamente inferiore: il die di Sandy Bridge ha poco meno di 1,2 miliardi di transistor ma occupa un'area di soli 216mm quadrati contro i 315mm quadrati di Vishera, nonostante il processo produttivo sia sempre a 32nm. E un miglioramento sarebbe auspicabile anche nelle fila di GF per poter accedere ad un processo produttivo più avanzato, chissà forse saltando direttamente ai 14nm. Ipotesi e possibilità tutte da verificare, ma intanto la situazione resta quella di un prodotto che sulla carta avrebbe grosse potenzialità ma nella pratica deve subire la concomitanza di numerose problematiche.

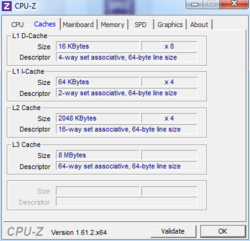

Anche riguardo l'organizzazione della memoria cache, altro tallone d'Achille per le CPU AMD rispetto alle proposte Intel, non troviamo alcuna differenza rispetto a Bulldozer. La gerarchia a tre livelli prevede una cache L1 dati esclusiva da 16KB per ogni core set associativa a 4-vie, una cache L1 istruzioni set associativa a 2 vie da 64KB per modulo, dunque condivisa fra due core, una cache L2 da 2MB per modulo, anch'essa condivisa fra due core, con set associatività a 16-vie ed infine una cache L3 da 8MB (per i modelli a 8-core) condivisa fra tutti i moduli.

Fin qui sembrerebbe che non ci siano novità di rilievo. Guardando a quanto indicato da AMD il diagramma a blocchi dell'architettura non subisce alcun intervento, cosa che invece accade all'interno dei singoli blocchi:

Blocchi dell'architettura di Bulldozer, identici a quelli di Vishera

Blocchi dell'architettura di Bulldozer, identici a quelli di Vishera

Le novità introdotte con Vishera

Le novità introdotte con Vishera

Le novità - come anticipato - sono tutte sotto forma di ottimizzazioni: quasi ogni singolo blocco dell'architettura Bulldozer è stato rivisto e migliorato per garantire maggiori prestazioni ed efficienza. Anzitutto il produttore si è preoccupato di migliorare gli algoritmi di branch prediction per avere un più basso penalty in caso di errore nella previsione e le unità di instruction retire. A ciò è seguito un ampliamento del modulo di decodifica ora in grado di supportare istruzioni FMA3 ed F16C ed una ottimizzazione degli scheduler per le istruzioni integer e floating point.

AMD ha lavorato anche al miglioramento dei registri e delle cache con modifiche agli algoritmi di prefetch, ampliamento della TLB della cache L1 e aumento dell'efficienza della cache L2.

| Latenza cache (cicli di clock) | ||||||

| Core i7 2600K | Core i7 3960X | Core i7 3770K | AMD Phenom II | AMD FX-8120 | AMD FX-8350 | |

| L1 | 4 | 3 | 3 | 3 | 4 | 4 |

| L2 | 11 | 10 | 10 | 16 | 27 | 25 |

| L3 | 36 | 64 | 54 | 86 | 88 | |

Tali modifiche hanno portato ad un leggero miglioramento della latenza della cache L2 che passa da 27 cicli di clock a 25 mentre resta invariata quella associata alla cache L1.

Come per le CPU Bulldozer, anche le nuove Vishera utilizzano la tecnologia Turbo Core per aumentare l'efficienza. Il Turbo Core permette il funzionamento a frequenze superiori rispetto a quella di default utilizzando due step indicati come All Core Turbo (tutti i core sono utilizzati e fatti funzionare ad una frequenza maggiore) e Max Turbo (un numero ridotto di core è utilizzato ad una frequenza ancora superiore).