Se Kaveri è accreditato del supporto alle memorie GDDR5M, l'APU che la seguirà potrebbe adottare una tecnologia d'interconnessione/interfaccia per le memorie 3 o 4 volte più veloce.

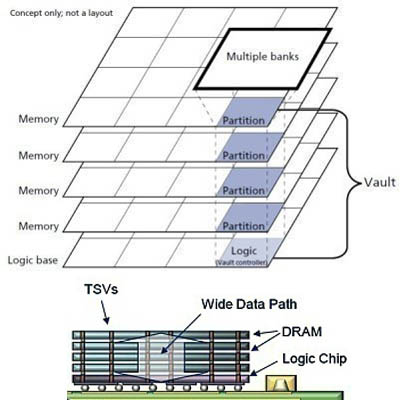

Parliamo della tecnologia HMC (Hybrid Memory Cube) che prevede n-strati di DRAM impilati e interconnessi tramite TSVs (through silicon vias), abbinati ad un più efficiente logica di controllo. Dopo 17 mesi di lavoro il consorzio che si occupa di tale tecnologia, guidato da Micron e che annovera tra i partecipanti anche AMD (anche se in maniera indiretta), ha finalmente ratificato le specifiche 1.0 dando il via libera alla realizzazione di DRAM stacked con capacità di 8GB in grado di raggiungere transfer rate di 320GB/s (Gigabyte al secondo). Prestazioni abissali se paragonate ai 22GB/s delle DDR3 in 2CH e sensibilmente superiori ai 96 GB/s ottenuti utilizzato chip GDDR5 funzionanti a 6GHz e abbinati ad un IMC di 128-bit, con in più il vantaggio di consumare meno.

Questa tecnologia dovrebbe concretizzarsi nel 2014.

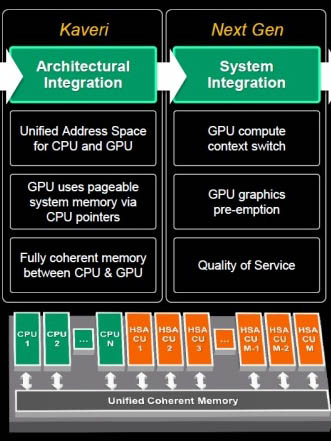

AMD sembra intenzionata ad utilizzarla per supportare al meglio le abilità HSA-full delle APU di futura generazione.