Architettura: CPU "Piledriver", iGPU "Devastator"

Le nuove APU A-Series per desktop sono disponibili in configurazioni con uno o due moduli x86 “Piledriver” a 32nm (due o quattro cluster/thread). L'architettura deriva da quella “Bulldozer” utilizzata da AMD per le CPU di fascia più alta della serie FX. Nello stesso die il produttore ha integrato una GPU della serie Radeon HD 7000 con supporto per le API DirectX 11, insieme ad un controller delle memorie, un controller PCI Express ed un Northbridge. A seconda dei modelli il TDP di queste soluzioni varia da 65W a 100W.

Le frequenze di funzionamento dei componenti interni alla APU sono regolate mediante la tecnologia AMD Turbo Core 3.0 che, nel rispetto del TDP e in base alle richieste dell'applicazione attiva, incrementa o diminuisce ora quelle dei core x86, ora quelle della iGPU.

Il memory controller di Trinity supporta moduli DDR3 fino a 1866MHz. L'architettura del core Piledriver, vista ad alto livello, non differisce molto da quella di Bulldozer dalla quale deriva ma rispetto ad essa prevede diverse ottimizzazioni che la rendono più veloce e più efficiente.

Come per Bulldozer, invece di due core completamente indipendenti ognuno dotato di risorse dedicate, un modulo Piledriver comprende due core x86 che condividono parte delle risorse, in particolare la FPU, la cache L2 e le unità per il recupero e la decodifica delle istruzioni (instruction retirement, registri di load/store).

Alle due ALU indipendenti, dotate ognuna della propria cache L1 dati, del proprio scheduler e delle proprie unità di calcolo, è affiancata una singola unità per i calcoli Floating Point che può gestire le istruzioni di uno dei due thread alla volta, condividendo la cache dati delle due ALU. L'ottimizzazione raggiunta in termini di occupazione di spazio e di banda dati dovrebbe ampiamente ripagare lo scotto prestazionale che comunque bisogna pagare quando si condividono delle risorse hardware.

Rispetto a Bulldozer, AMD ha apportato delle ottimizzazioni al front end utilizzando un design più aggressivo. Lo stesso concetto è stato applicato alla logica flip-flop per garantire una sensibile riduzione dei consumi.

AMD afferma che altri miglioramenti sono stati apportati alle unità di calcolo floating point ed integer, a quelle di branch prediction e prefetch. Il blocco di branch prediction include una nuova unità che tiene conto della storia e lavora in parallelo con l'unità già presente in Bulldozer (e sulla quale ha priorità), mentre il blocco di prefetch di Piledriver segna i dati di prefetch non usati come quelli meno recenti al contrario di Bulldozer, evitando che vengano ricaricati inutilmente.

In Piledriver sono state poi aggiunte le nuove istruzioni FMA3 (in Bulldozer era stato integrato il supporto per le FMA4) ed F16C, in aggiunta a quelle AVX, AVX 1.1 ed AES, per allinearsi all'ISA di Haswell.

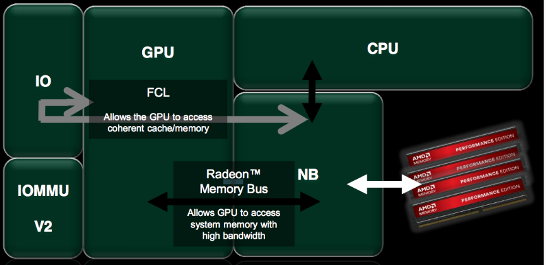

Trinity dispone di un bus a 256-bit bidirezionale per ogni memory channel, denominato RMB (Radeon Memory Bus), per l'accesso diretto ai controller DRAM da parte della iGPU e utilizza la seconda versione dell' IOMMU (Input/Output Memory Management) per supportare la condivisione sicura ed efficiente della memoria virtuale x86 della CPU.

Abbiamo raccolto le specifiche tecniche nella seguente tabella:

| Specifiche APU AMD Trinity | ||||

| AMDTrinity | AMD Llano | Intel Sandy Bridge | Intel Ivy Bridge | |

| Socket | FM2 | FM1 | LGA 1155 | LGA 1155 |

| Transistor | 1,303 miliardi | 1,178 miliardi | 995 milioni | 1,4 miliardi |

| Processo produttivo | 32nm SOI | 32nm SOI | 32nm | 22nm |

| Dimensioni die | 246mm2 | 228mm2 | 216mm2 | 160mm2 |

| Cache L1 | 128 KB per core | 128 KB per core | 64 KB per core | 64 KB per core |

| Cache L2 | 2MB per modulo | 1MB per core | 256 KB per core | 256 KB per core |

| Cache L3 | N/A | N/A | 8 MB | 8 MB |

| Core / Thread | 4/4 | 4/4 | 4/8 | 4/8 |

| Turbo | Si | Si | Si | Si |

| FPU | 128-bit | 128-bit | 128-bit | 128-bit |

| Controller memorie | - DDR3-1866 - Dual-channel |

- DDR3-1866 - Dual-channel |

- DDR3-1333 - Dual-channel |

- DDR3-1600 - Dual-channel |

| Controller grafico | - Radeon series - DirectX 11 - UVD3 |

- Radeon series - DirectX 11 - UVD3 |

- Intel HD Graphics - DirectX 10.1 - Quick Sync |

- Intel HD Graphics - DirectX 11 - Quick Sync |

| Controller PCI Express | 16 linee | 16 linee | 16 linee | 16 linee |

| Risparmio energetico | - Più stati low-power - PCIe core power gating - PCIe speed power policy - GPU e video decode (UVD3) power gating - AMD Turbo Core 3.0 |

- Più stati low-power - PCIe core power gating - PCIe speed power policy - GPU e video decode (UVD3) power gating - AMD Turbo Core (ove previsto) |

- Più stati low-power - CPU core power gating - GPU power gating - Turbo Boost (ove previsto) |

- Più stati low-power - CPU core power gating - GPU power gating - Turbo Boost (ove previsto) |

| TDP | 65W e 100W | 65W e 100W | 65W e 95W | 65W e 77W |

La GPU integrata riveste ancora una volta il ruolo principale nelle APU AMD ed occupa gran parte dell'intero die di Trinity. Conosciuto con il nome in codice di "Devastator" il chip grafico continua a supportare le API DirectX11 insieme alla funzione di tesselation ed è compatibile con le ultime tecniche di filtraggio (MLAA, FXAA)

Dal punto di vista del design i tratta di una GPU che deriva dall'architettura Cayman (ALU di tipo VLIW4) utilizzata da AMD sulle schede video discrete Radeon HD 6900-series. Ovviamente è stata depotenziata come numero di Stream Processor, TMUs e ROPs ed ha visto sul front-end la rimozione del dual-graphic engine in favore di un'unità singola per i calcoli geometrici e sul back-end il netto taglio del controller delle memorie.

Nella variante più potente l'iGPU "Devastator" integra 384 Stream Processors organizzati in 6 SIMDs. E' la prima volta che vediamo un design VLIW4 realizzato con il procesos produttivo a 32 nanometri di GlobalFoundries (Cayman era realizzato con tecnologia a 40nm di TSMC) e questo ha consentito ad AMD di aumentare l'efficienza di funzionamento rispetto ai 400 Stream Processors VLIW5 (organizzati in 5 SIMDs) presenti dell'iGPU "Sumo" di Llano, a parità di processo produttivo.

(Diagramma a blocchi delle iGPU "Devastator")

Sotto il profilo della decodifica video, AMD ha integrato in Trinity un completo blocco UVD3/VCE simile a quello visto nelle GPU discrete che permette di accelerare la codifica e decodifica dei flussi video in alta definizione nei formati H.264, VC1, DivX e XviD.