AMD finalmente ci svela alcune succose novità riguardo Zen, ed in parte conferma quanto avevamo preannunciato nei mesi scorsi. Comunque, poiché non siamo stati invitati all'evento, non possiamo descrivervi quanto detto dai dirigenti della casa di Sunnyvale, quindi dobbiamo necessariamente appoggiarci a fonti esterne. Un buon punto di partenza è sicuramente Ian Curtress di Anandtech, e proprio per questo vi invitiamo a leggere il suo approfondimento.

Tornando a noi, possiamo affermare quanto segue:

- come da noi preannunciato, Zen avrà un IPC molto simile a Broadwell, ed AMD ce lo conferma in questo confronto (Normalizzato a 3 GHz) tra Zen (8c/16t) e Broadwell-E (8c/16t) utilizzando il software “Blender”;

- Zen è effettivamente velocissimo, come ci era stato detto dopo l'addio di Jim Keller, nonostante in molti fossero scettici;

- la cache rinnovata è effettivamente a bassa latenza, come ci suggerisce anche Dresdenboy sul proprio blog;

- l'uArch di Zen è stata sviluppata sulla falsariga di quelle Intel, al fine di sfruttare le ottimizzazioni dei compilatori.

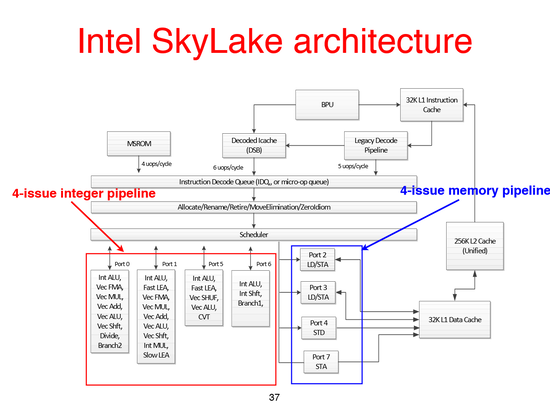

Questi fatti ci portano ed effettuare alcune considerazioni, e partiremo proprio da quest'ultimo punto. La prima considerazione infatti riguarda la volontà di AMD di “emulare” le uArch di Intel, al fine di evitare la necessità di avere software scritto ad hoc (cosa impossibile quando si ha un market share così basso). Possiamo notare dai grafici qui in basso come l'organizzazione di Zen sia molto simile a quella di Skylake (Ad esempio la gestione delle micro-op queue). In questo modo AMD potrà sfruttare fin da subito il software scritto per le CPU Intel, senza dover necessariamente aspettare ottimizzazioni (Ad esempio, la patch per il CMT di Microsoft).

La Cache L1 sembra riprendere in parte le idee che si erano sviluppate con la CPU ad alte prestazioni Alpha 21264, con una “Separate primary cache” in grado di garantire basse latenze e prestazioni elevate. Confrontiamo quanto scrive Ian sulla cache L1 di Zen con quanto è scritto su Wikipedia.org sulla cache L1 dell'Alpha 21264 (L'ultima creatura di Jim Keller in DEC), la quale si sarebbe dovuta utilizzare anche sugli Alpha 21364 e 21464 (Questi ultimi due cancellati da Compaq per portare avanti il progetto Itanium insieme ad Intel).

Ian: “The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come”.

Wikipedia: “The primary cache is split into separate caches for instructions and data, the I-cache and D-cache respectively. Both caches have a capacity of 64 KB. The D-cache is dual-ported by transferring data on both the rising and falling edges of the clock signal. This method of dual-porting enabled any combination of reads or writes to the cache every processor cycle. It also avoided duplication the cache so there are two, as in the Alpha 21164. Duplicating the cache restricted the capacity of the cache, as it required more transistors to provide the same amount of capacity, and in turn increased the area required and power consumed”.

In ultimo, come già affermato, aspettiamoci frequenze di clock molto vicine ai 4 GHz, e la possibilità che AMD torni a commercializzare processori mainstream con il moltiplicatore bloccato, lasciando quello sbloccato solo a modelli (Black Edition?) dal prezzo più elevato. L'IHS, con tutta probabilità, sarà saldato.

Nel mese di Settembre pubblicheremo un corposo speciale dedicato a Zen, in cui inseriremo anche alcune impressioni delle nostre immancabili fonti anonime che lavorano presso importanti OEM, oltre a dati che AMD rilascerà durante l'imminente Hot Chips. ;)