Architettura della GPU Bonaire: GCN 1.1 alza la testa

Bonaire ha un die di 160 millimetri quadrati ed ospita 2,08 miliardi di transistor. Confrontato con Pitcairn è più piccolo del 32% e paragonato con Cape Verde è più grande del 30%.

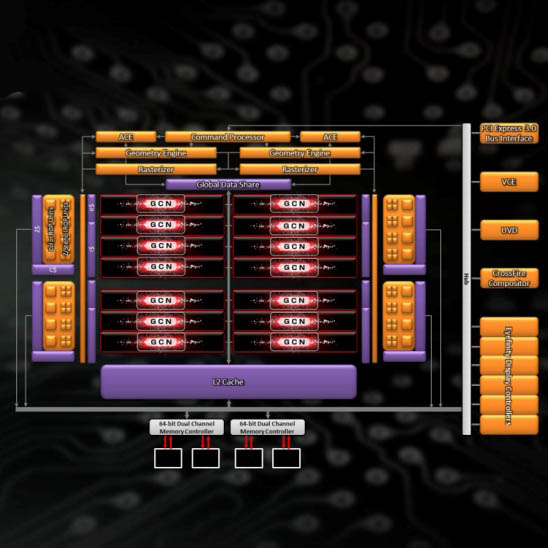

Se con Pitcairn AMD ha sostanzialmente preso tutte le unità funzionali di Cape Verde e le ha raddoppiate, con Bonair AMD ha utilizzato un procedimento "intermedio" creando un ibrido tra le due architetture.

Come detto in precedenza il front-end è quello di Pitcairn (o di Tahiti), cioè presenta due geometry engines separati (ognuno dotato dei blocchi fondamentali di Geometry, Tessellation e Rasterizer) e per questo è in grado di processare due triangle per clock rispetto all'elaborazione singola di Cape Verde. Quest'implementazione consente a Bonaire di affrontare a testa alta la GPU GK106-220 della GTX 650 Ti anche negli scenari di tessellation più impegnativi (ricordiamo che Nvidia ha spostato l'elaborazione di vertici e primitive direttamente all'interno del GPC).

Lo shader engine è basato su design GCN con 896 SPs suddivisi in due cluster con un'organizzazione a 4+3 array di CU (ricordiamo che Cape Verde utilizza un singolo cluster a 4+3+3 array, mentre Pitcairn due cluster con la medesima configurazione di Cape Verde).

Il back-end deriva invece da Cape Verde: troviamo 16 ROPs (contro le 32 di Pitcairn) e due memory controller da 64-bit (contro i quattro di Pitcainr). Per bilanciare un bus ampio appena 128-bit AMD è stata costretta ad utilizzare dei velocissimi chip VRAM GDDR5 funzionanti a 1500 MHz (6000 MHz effettivi). In questo modo la bandwidth messa a disposizione dalle memorie per la GPU Bonaire è salita a 96 GB/s (contro i 72GB/s destinati a Cape Verde). Valore comunque lontano dai 153 GB/s di Pitcairn, che ricordiamo può contare su un bus da 256-bit).

(clicca sui pulsanti per confrontare le architetture)

Bonaire supporta l'ISA (Instruction Set Architecture) della generazione Sea Islands: offre cioè nuovi meccanismi di accesso alla memoria unificata tra CPU/GPU, code aggiuntive ed un maggiore parallelismo tra le compute pipeline rispetto alle GPU della serie Southern Islands.

Di seguito riportiamo il primo documento riguardante l'ISA per l'architettura Sea Islands (indicata con l'acronimo C.I) che evidenzia le differenze rispetto a Southern Islands (S.I):