Bulldozer concept

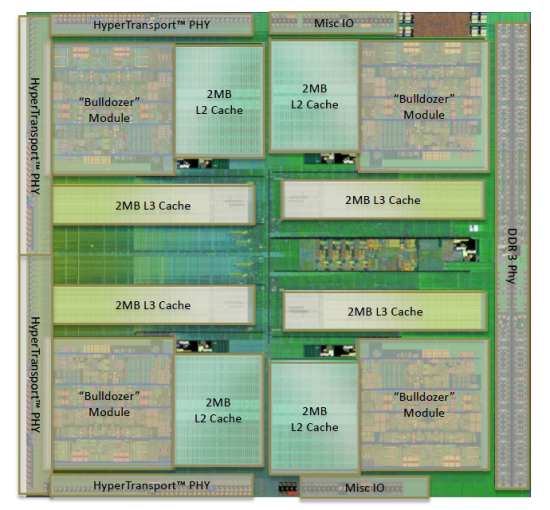

Bulldozer è il nome scelto da AMD per indicare l'architettura delle CPU di nuova generazione che introducono per la prima volta il concetto di modulo contrapposto a quello di core di una tipica CPU x86 multi-core. Le attuali soluzioni raccolte sotto il marchio "FX" recano il nome in codice di Zambezi e sono disponibili in configurazioni a 8-, 6- e 4-core, utilizzando rispettivamente 4, 3 e 2 moduli.

| Caratteristiche di base delle CPU in esame | |||||

| AMD Zambezi (8-core) |

Gulftown (6-core) |

Intel SB (4-core) |

Intel SB-E (6-core) |

Intel IB (4-core) |

|

| Socket | AM3+ | LGA 1366 | LGA 1155 | LGA 2011 | LGA 1155 |

| Numero di transistor | ~2 miliardi | 1,17 miliardi | 1,16 miliardi | 2,27 miliardi | 1,4 miliardi |

| Processo produttivo | 32nm SOI GF | 45nm | 32nm | 32nm | 22nm |

| Dimensioni die | ~315mm2 | 239mm2 | 216mm2 | 435mm2 | 160mm2 |

| Cache L1 | 16KB D per core 64KB I per modulo |

32KB D per core 32KB I per core |

32KB D per core 32KB I per core |

32KB D per core 32KB I per core |

32KB D per core 32KB I per core |

| Cache L2 | 2MB per modulo | 256KB per core | 256KB per core | 256KB per core | 256KB per core |

| Cache L3 | 8MB | Fino a 12MB | 8MB | Fino a 15MB | 8MB |

| Thread per core | 1 | 2 | 2 | 2 | 2 |

| Turbo | Si | Si | Si | Si | Si |

| FPU | 256-bit | 128-bit | 128-bit | 128-bit | 128-bit |

| Controller delle memorie | DDR3-1866 Dual-channel |

DDR3-1066 Triple-channel |

DDR3-1333 Dual-channel |

DDR3-1600 Quad-channel |

DDR3-1600 Dual-channel |

| Controller grafico | N/A | N/A | DirectX 10.1 | N/A | DirectX 11 |

| PCI Express | N/A | N/A | 16 lane (2.0) | 40 lane (3.0) | 16 lane (3.0) |

| TDP | 95W, 125W | 130W | 65W, 95W | 130W | 77W |

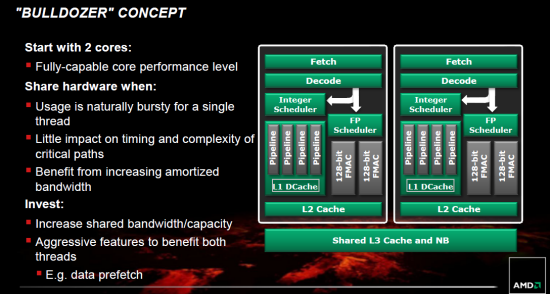

Con il modulo Bulldozer viene meno quella totale indipendenza fra core e parte delle risorse vengono condivise. Nel percorso di avvicinamento a BD, AMD è partita con due core completamente separati ed ha cominciato a fondere assieme alcune parti guardando da un lato al guadagno in termini di efficienza e dall'altro al rate di utilizzo di quelle parti stesse.

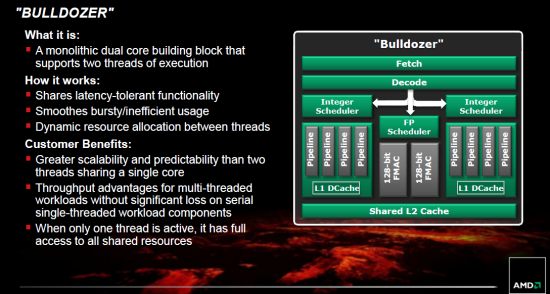

I due core indipendenti si sono così trasformati in un modulo Bulldozer, mattoncino di base per tutte le CPU AMD FX. Al suo interno i due core condividono la cache L2, la FPU - che ora è più complessa ed è in grado di gestire anche istruzioni FMAC a 256-bit - e le unità per il recupero (Fetch) e la decodifica (Decode) delle istruzioni. Ogni core dispone in maniera esclusiva, invece, della cache L1 e dell'unità di calcolo Integer.

A differenza di Intel, AMD ha fornito ogni modulo di un elevato quantitativo di cache L2: i numeri dicono che nelle CPU Ivy Bridge sono presenti 256KB di cache L2 per ogni core, per un totale di 2MB. Nelle CPU Bulldozer ogni modulo dispone di 2MB di cache L2 (condivisi fra i due core del modulo stesso) per un totale di 8MB nelle configurazioni a 8-core.

La politica di gestione delle cache pensata da AMD dovrebbe fornire eccellenti risultati sulla carta e invece dall'esperienza sappiamo bene essere molto più efficiente ed aggressiva l'idea della rivale Intel.

Bulldozer prevede una gerarchia a 3 livelli, come per Sandy Bridge ed Ivy Bridge, ma ogni singolo livello è stato ripensato per accomodare l'idea di modulo a due core. La cache L1 è nettamente suddivisa in due parti ove una porzione a 4-vie set associativa di 16KB per ogni core è destinata ai dati (insieme ad una TLB da 32 voci per eseguire due operazioni di load ed una di store su operandi a 128-bit per ciclo) ed una porzione da 64KB (condivisa fra i due core di ogni modulo) è destinata alle istruzioni.

Anche la cache L2 è condivisa fra i due core dello stesso modulo e prevede una set associatività a 16-vie con TLB ampia 1024 voci. La cache L3 di tipo set associativa a 64-vie è condivisa fra tutti i moduli di Bulldozer.

AMD ha inoltre apportato sensibili modifiche al Front End di Bulldozer grazie al quale riesce a decodificare fino a 4 istruzioni per ciclo di clock ed alla FPU (Floating Point Unit) che integra due unità FMAC a 128-bit ma che risulta essere condivisa fra i due core. O meglio, mentre sono presenti due unità di elaborazione per gli interi all'interno di ogni modulo, di unità FPU ne troviamo una sola. A livello di singolo modulo la complessità è stata ridotta ma al contempo ogni unità FPU è stata potenziata rispetto al passato (Phenom II) quando non era in grado di gestire le nuove istruzioni AVX a 128-bit o a 256-bit.

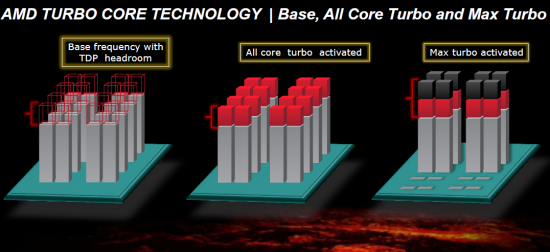

Per aumentare l'efficienza AMD ha seguito le orme tracciate da Intel con la tecnologia Turbo proponendo una versione che, pur mantenendo lo stesso obiettivo, si discosta da quella della rivale per come è stata implementata.

Il Turbo Core delle CPU Bulldozer fa sì che essa possa funzionare a frequenze superiori a quella "Base" fino a che non venga raggiunto il massimo valore di TDP. Fino a che c'è spazio in tal senso, in presenza di un'applicazione fortemente multi-threaded, tutti i core possono essere fatti funzionare ad una frequenza più elevata di quella nominale (All Core Turbo). Se sul sistema sta girando un'applicazione single-core o poco ottimizzata per il multi-thread, allora solo alcuni core sono attivi e la loro frequenza di funzionamento può essere ulteriormente innalzata (Max Turbo).