Zen, e più ancora Zen2, come abbiamo avuto modo di riportare nel paragrafo precedente, nascono soprattutto per venire incontro alle esigenze del mercato Server e solo in un secondo momento alle esigenze del mercato Consumer. Proprio per questo si è reso necessario l'utilizzo del protocollo di comunicazione PCI-E 4.0, al posto dell'ormai antiquato PCI-E 3.0, in combinazione con la tecnologia Infinity Fabric 2 (in grado di garantire latenze molto più basse rispetto alla prima iterazione). Le CPU EPYC "Rome" (Zen2) avranno il doppio dei core delle CPU EPYC "Naples" (Zen) e per fornire un'adeguata banda passante (Soprattutto in sistemi 2S) il PCI-E 3.0 sarebbe stato insufficiente. Per fare un confronto, la banda di trasferimento PCI-E 4.0 tra CPU arriva a 31,5 GB/s, mentre la banda di trasferimento del protocollo di comunicazione QuickPath Interconnect di Intel si ferma a 25,6 GB/s.

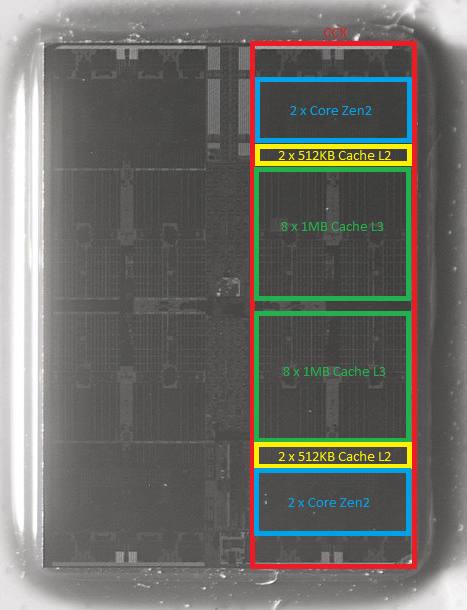

AMD, per rendere il tutto più semplice da produrre, ha deciso di integrare nel Die Zen2 (denominato CCD - Core Chiplet Die) il minimo necessario, come è possibile osservare dallo schema realizzato sulla foto del Die di Zen2 (Fonte: Fritzchens Fritz), sfruttando al massimo il design Chiplet (nome più commerciale della tecnologia MCM - Multi Chip Module). Addio ai CTRL DDR4, ai CTRL SATA e a molto altro On-Die. Tutto ciò ha permesso di realizzare un Die snello (74mm2), semplice da produrre in cui la possibilità di incorrere in difetti è ridotta al minimo. Questo, quindi, garantisce una resa produttiva molto elevata (Già oggi siamo oltre all'85% su un processo moderno come i 7nm di TSMC).

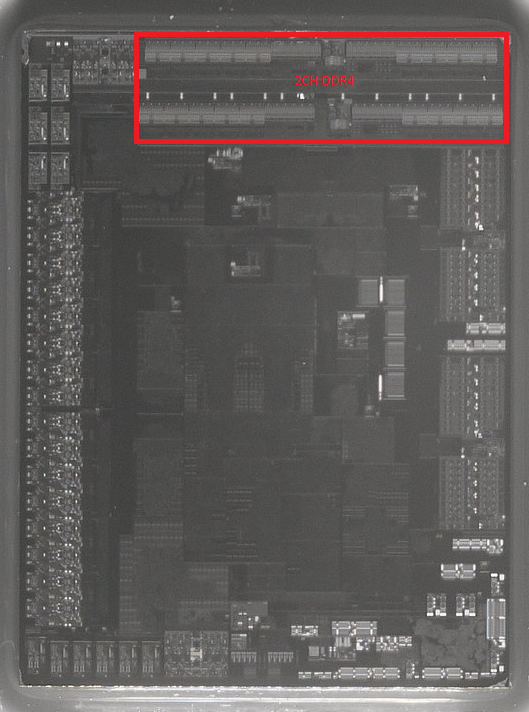

Nel chip di I/O (Chiamato da AMD "I/O Die"), invece, possiamo notare il CTRL DDR4 Dual Channel, oltre a tutto quanto concerne la connettività: connessioni PCI-E 4.0, 2 porte SATA III, il CLOKGEN, 4 porte USB 3.1 Gen2, le connessioni Infinity Fabric 2, ecc. Questo chip è prodotto a 12nm presso GlobalFoundries, e grazie alle ottime rese produttive raggiunte da questo nodo risulta anche molto economico da produrre.

Come già detto, tutto ciò è stato reso possibile dall'utilizzo del protocollo di comunicazione PCI-E 4.0. Osservando le slide qui di seguito, il design delle CPU EPYC2 (Rome) risulta ora molto semplice rispetto a quello delle CPU EPYC (Naples). Per il mercato Consumer l'utilizzo del PCI-E 4.0 non sarebbe stato essenziale, ma si è comunque deciso di mantenerlo per una sorta di continuità: realizzare ex-novo un altro I/O Die solo per sfruttare il PCI-E 3.0 sarebbe stato uno spreco di denaro, in quanto il PCI-E 4.0 è retrocompatibile con lo standard 3.0. Inoltre, utilizzare il PCI-E 4.0 avrebbe portato un notevole vantaggio sulle piattaforme Consumer ed Enthusiast nei confronti di Intel. Ad esempio, la piattaforma AM4 di AMD è l'unica in grado di sfruttare adeguatamente gli SSD M.2 NVMe PCI-E 4.0.